Research

During my undergraduate degree in EE at IIT Madras, I delved into a range of projects revolving around Semiconductor Device Physics, Integrated Circuits and Systems, Photonics, Communication and Signal Processing.

Estimating Memory Cost

Modern computing systems are power hungry. Recent studies have shown that the energy consumption is rising at an alarming rate calling for the development of energy efficient computing paradigms, devices and circuits. This has led to the development of Neuromorphic computing and Probabilistic Computing. Recent literature also hints at the emergence of computing systems and devices inspired from human biology.

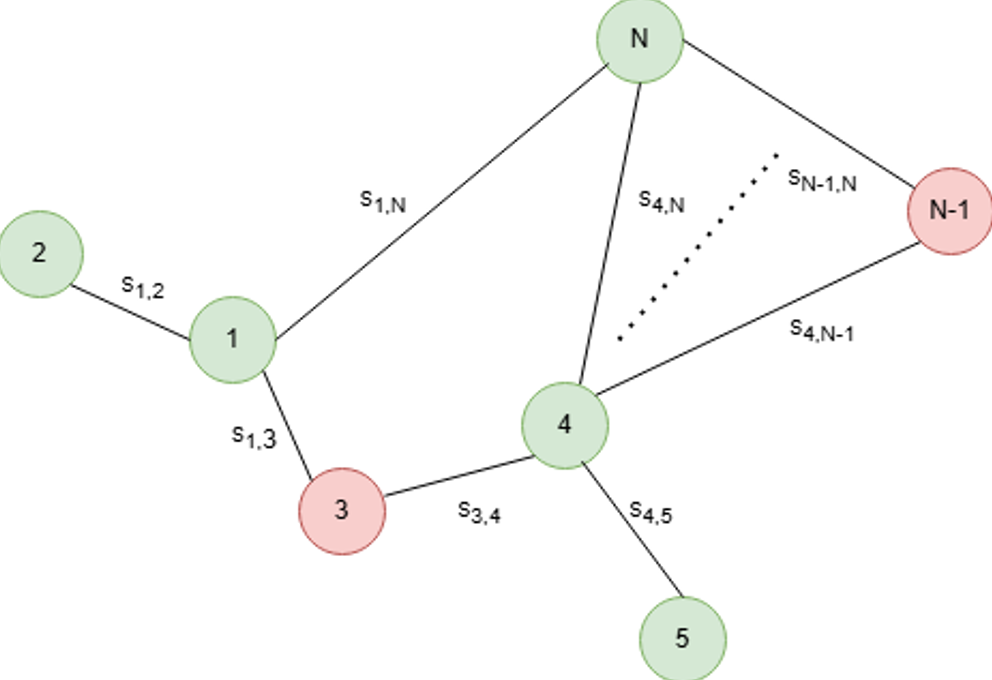

Starting my sophomore year, I worked on developing a theoretical framework to estimate the energy expenditure of a memory block drawing inspiration from Markov Chains, Ising Model from Statistical Physics and Economics. I have been fortunate to collaborate with Prof. Anjan Chakravorty, Prof. Avhishek Chatterjee and Prof. Bhaswar Chakrabarti on this exploratory problem statement.

Our work on the same can be found on arXiV. Links to the same are attached below. I was awarded the Valadi Krishna Sarma Balaji & Savithri Balaji Award for the Best Thesis on Power/ Energy Savings across all degrees (B.Tech, M.Tech, M.S. and PhD) for my work on “Estimating Memory Cost” at the 62nd Convocation of IIT Madras.

Related Paper : Stochastic Analysis of Retention Time of Coupled Memory Topology

AI Circuits and Circuit Design Automation

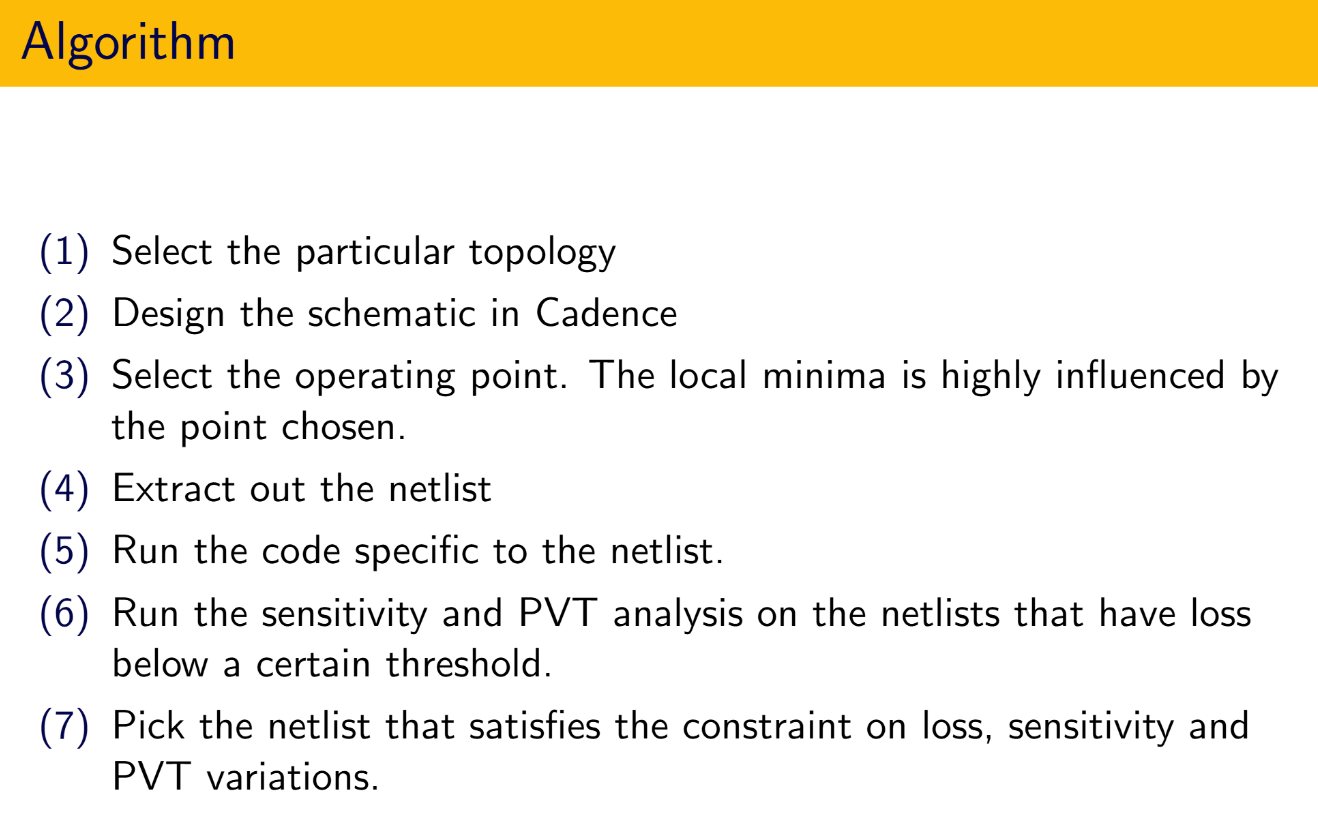

Circuit Design and Machine Learning are an interestingly correlated duo. To improve the compute resources required for running Large Language Models (LLMs), we require that ICs are fabricated more quickly and efficiently and are also energy efficient. The traditionl IC Design route is often long and tiring ranging from 6 months to over an year. The efficient use of ML algorithms such as Gradient Descent and Reinforcement Learning can make this process faster.

To explore how ML algorithms can improve IC Design techniques, I collaborated with Prof. Sankaran Aniruddhan during my Junior year at IIT Madras. Our work on the same is published in IEEE and was presented at MWSCAS’ 25 at Michigan.

Elegant circuit design principles can help in designing better AI hardware. During Fall 24, I enrolled in Neuromorphic Computing to learn about efficient circuit design techniques to accelerate Machine Learning Hardware. Is the future of AI in analog computing? Learn more here.

Integrated Circuit (IC) : Design and Testing

During my stay at IIT Madras and Texas Instruments, I worked on a variety of Integrated Circuit Design and Testing (commonly abbreviated as ICDT) projects. My contribution in chip design projects ranged from schematic design to pre-tapeout layout design. Some of the designs I worked on are briefly described below:

1. Design of a Programmable X band Filter (9 GHz to 10 GHz)

This project revolved around designing an on-chip filter with a very high selectivity (High Q) and very high input power handling capability. The challenge involved in this design arises due to the low Q of the on chip inductors that need to be compensated for. During my stay at the High Speed Converters (HSC) group at Texas Instruments, I explored several design routes for the realization of such a high Q on-chip filter. This design was completed at a schematic level.

2. Design of a 50 GHz Continuous Time Linear Equalizer for an ADC frontend

This was my second challenging project at Texas Instruments where I was exposed to the world of Broadband circuits and Serial Links. My responsibilites here involved the design of a Continuous Time Linear Equalizer (CTLE) with a 50 GHz bandwidth and 50 dB linearity for an ADC frontend. The challenge involved in this design was to tackle the high capacitive load of the ADC at 50 GHz. This design was completed at a schematic level.

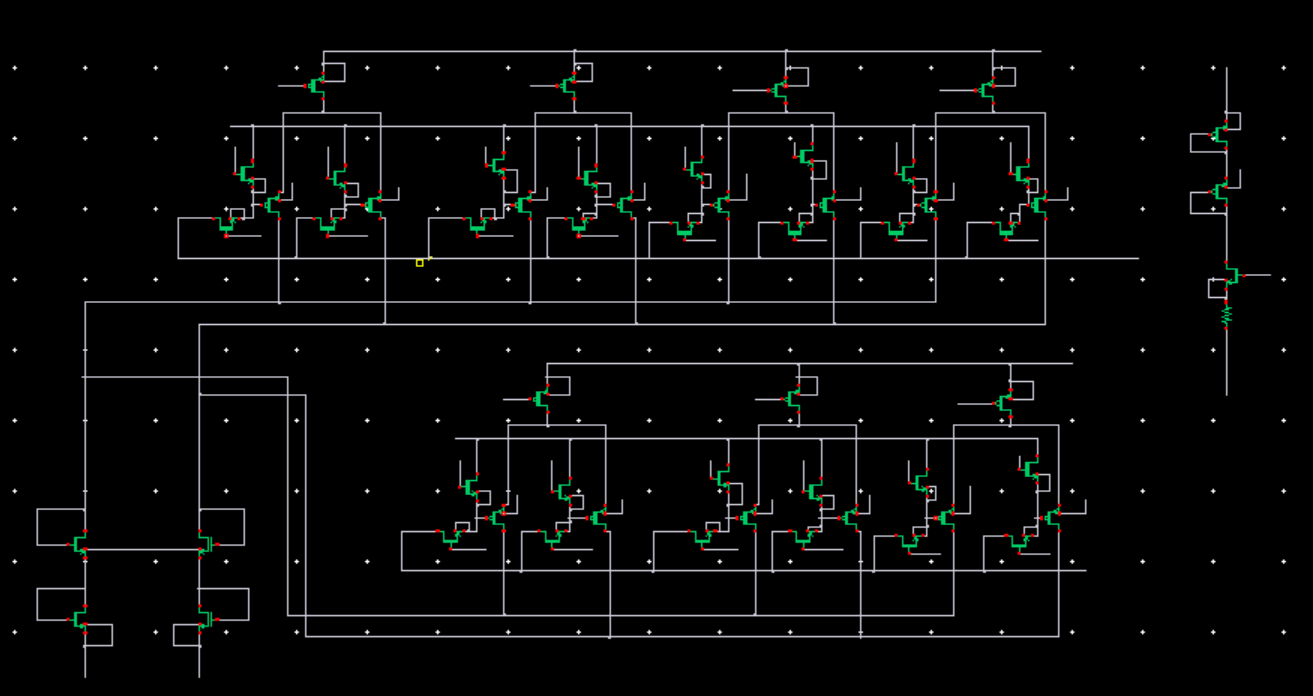

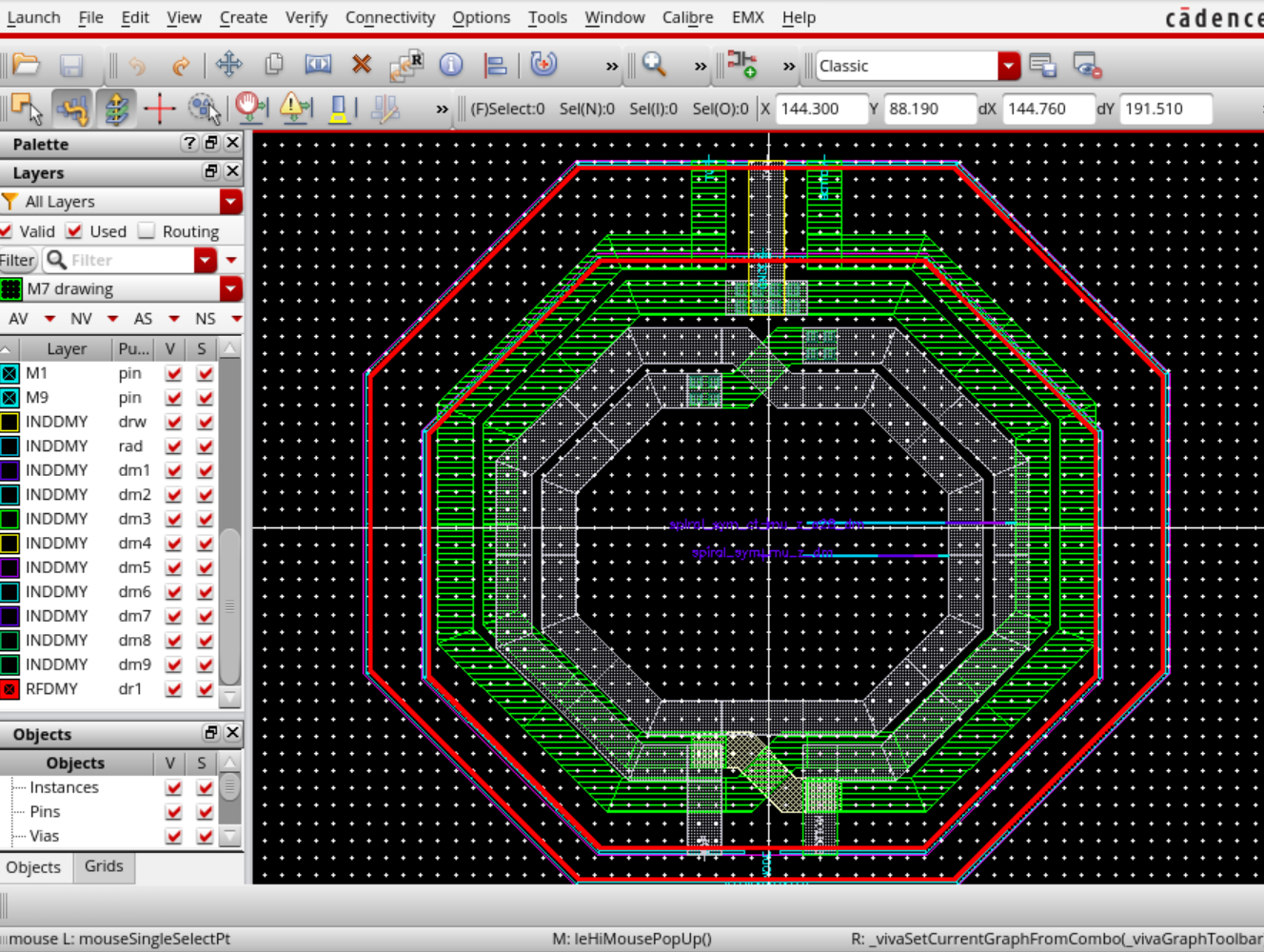

3. Design of a 6-bit Ku Band Phase Shifter

During my final year at IIT Madras, I collaborated with Prof. Sankaran Aniruddhan to design an Active Vector Summation based Phase Shifter for Ku-Band from 10 GHz to 15 GHz with an output P1dB of +5dBm in 28nm CMOS for beamforming applications. The design process involved several challenges - designing the transformer balun with required insertion loss to ensuring the DNL of the phase shifter was as required. Layout of several blocks were completed and the schematic design was closed. This phase shifter is now being designed as a part of a larger beamformer for 6G use.

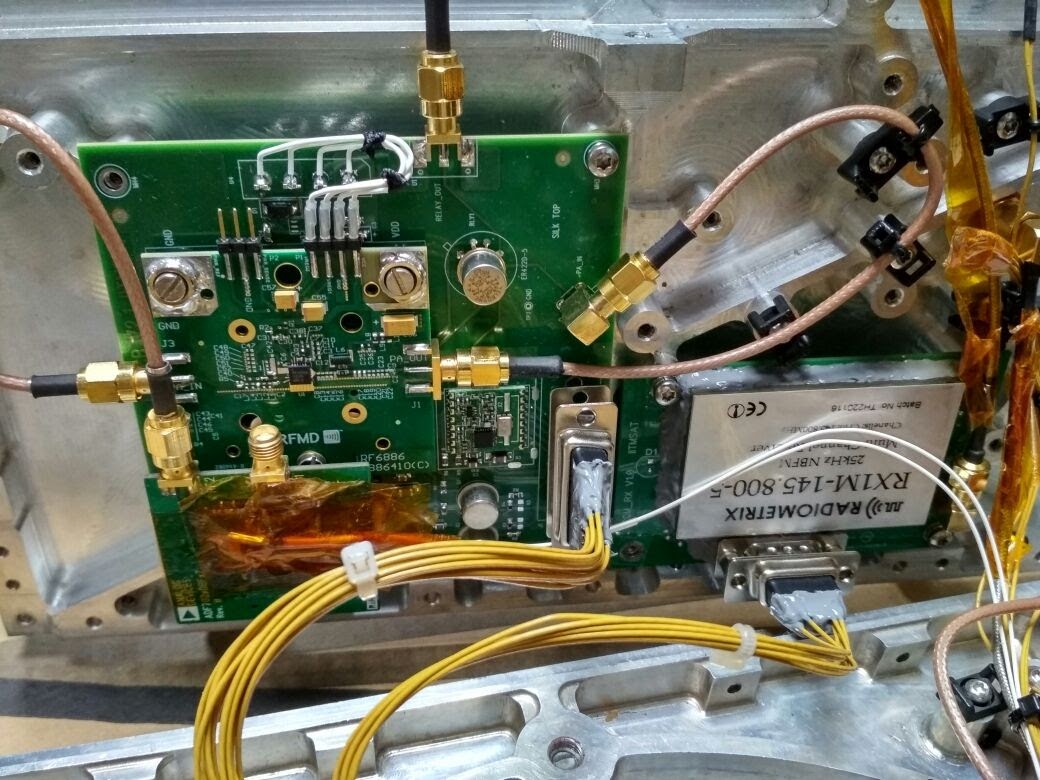

4. Testing of RF Circuital Blocks and PCBs

During my stay at IITMSAT, I got to test space grade PCBs and work with state-of-the-art network analysers to characterise amplifiers and splitters in the RF chain. I am incredibly grateful to Prof. David Koilpillai for providing me the opportunity to be a part of IITMSAT and letting me grow both personally and professionally in a collaborative environment.

Compact SPICE Modelling of Photonic Components

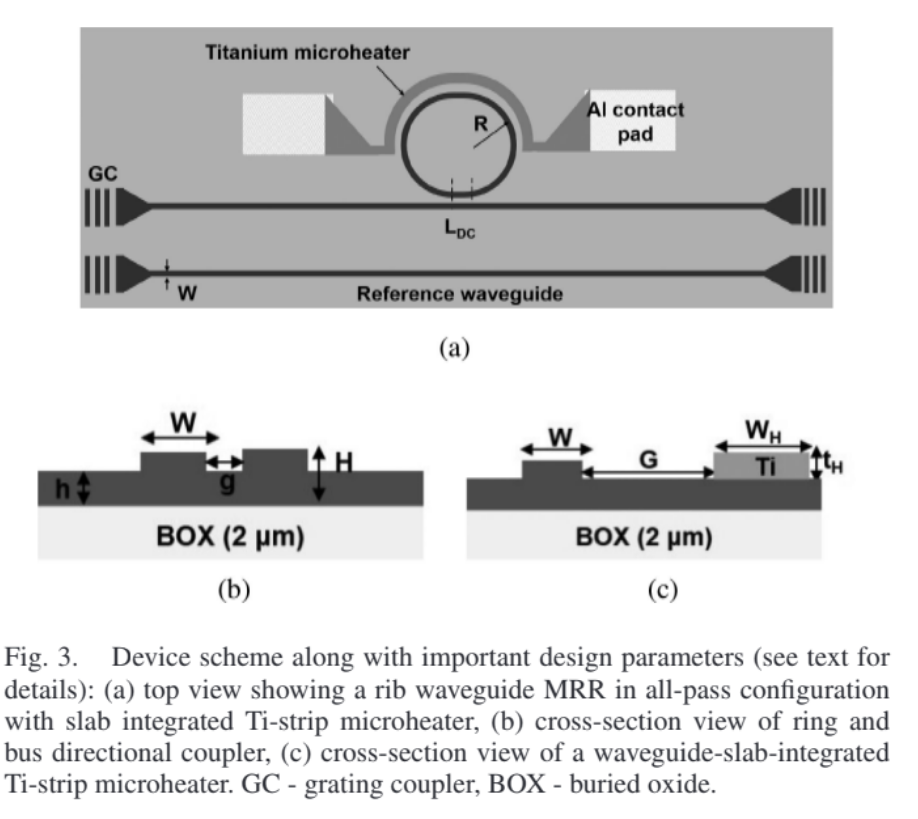

During my last year at IIT Madras, I worked on Silicon Photonics. My work involved developing compact SPICE models for photonic components on a Photonic Integrated Circuit (PIC). I was associated with the Center for Programmamble Photonic Integrated Circuits (CPPICS) at IIT Madras and was advised by Prof. Anjan Chakravorty. With the requirement of high bandwidth, low latency, low energy consumption systems for AI, Silicon Photonics has emerged as a popular choice for interconnects on a die. Modelling of such photonic components holds much value as it provides a circuit designer (photonic IC designer here) with insight to size passives and actives optimally for desired operation.